## 100V Surge Stopper Protects Components from 300V Transients

Hamza Salman Afzal

High voltage transients in automotive and industrial systems are common and can last from microseconds to hundreds of milliseconds, sending significant energy downsteam. Transient causes include automotive load dumps, and spikes caused by load steps and parasitic inductance. To avoid the risk of failure, all electronics in these systems must either be robust enough to directly withstand the transient energy spikes, or they must be protected from them.

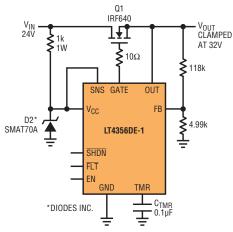

The LT4356 surge stopper is a dramatic performance upgrade over traditional, passive clamp protection techniques. It actively protects downstream components from overvoltage by regulating the gate of a pass MOSFET and it limits current with the help of a standard sense resistor. Figure 1 shows a typical 12V application.

The LT4356 has a rated maximum of 100V with an operating voltage range of 4V to 80V, making it ideal for protecting downstream electronics in a wide variety of industrial and automotive applications. Nevertheless, some circuits require protection against transients as high as 200V to 300V.

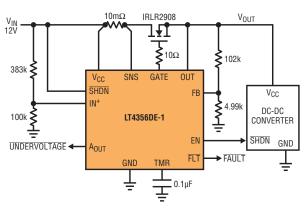

Figure 2 shows one way that the LT4356 can be made to suppress such high voltages, but at the cost of the current limiting feature. In Figure 2 the  $v_{CC}$  and SNS pins are decoupled from the raw input voltage and separately clamped to a safe value below 100V. Since the  $v_{CC}$  and SNS pins are of necessity disconnected from the input path, current sensing is not possible and the circuit serves only as a voltage clamp.

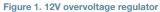

It is possible to overcome this limitation by cascading a second pre-regulating MOSFET, Q2, as shown in Figure 3. Q2 clamps the  $v_{CC}$  and SNS pins to a safe level, restores the current limit feature and as an added benefit, shares SOA (safe operating area) stress with Q1.

When power is first applied, R3 and D1 pull up on the gate of Q2, which in turn passes power through to the LT4356. The GATE pin then pumps up the gates of Q1 and Q2, fully enhancing both MOSFETS

and sending power through to the output. Thus R3 and D1 are critical to start-up. Under normal operating conditions the GATE pin limits itself to about 12.5V above the output, so with 12V at the input, Q1's gate is biased to 24.5V and Q2's gate is biased slightly lower, about 24V.

When the input is subjected to a high voltage transient, R3 and D1 pull up on the gate of Q2, which in turn is clamped by D2 to approximately 80v. Acting as a source follower, Q2's source rises no further than about 75v, keeping  $v_{CC}$  and sNs safely below their 100v maximum rating. Unlike the shunt clamped application shown in Figure 2, the series clamped topology of Figure 3 permits full use of the LT4356's current limiting feature. Q1 regulates in the normal way, limiting the output voltage as prescribed by R1 and R2.

An added benefit of the topology shown in Figure 3 is that Q2 shares SOA stress with Q1. For inputs in the range of 150V to 200V, the SOA stress is shared equally between Q1 and Q2. In certain applications this allows two inexpensive

The LT4356 has a rated maximum of 100V with an operating voltage range of 4V to 80V, but a little extra circuitry enables it to protect against transients as high as 300V.

MOSFETs to replace a single, and much more costly, special high soA device. As the peak input voltage requirement rises above 200V, the SOA becomes increasingly concentrated in Q2 and the series connection offers no substantial relief.

Figure 4 shows a complete circuit based on the new topology, designed to withstand up to 300v peak input. As previously

**\$**<sup>R3</sup>

10k

D1

1N4148

D2 /

SMAJ70A\*

\*DIODES INC.

VIN MAX BANGE: 0V-300V

0.1uF

OPERATING RANGE: 9V-16V

described, Q2's gate is clamped at 80v so that with a 300v input, Q2 drops 225v, while Q1 sees no more than 75v total. For this reason a 250v device is specified for Q2, and a 100v device suffices for Q1. It is possible to withstand even higher input voltages by appropriate selection of Q2.

When designing circuits to withstand such high input voltages, it is important

> Q1 FQB55N10

to recognize the potential for high dv/dt at the input and resulting consequences. Until the circuit can respond, current arising from an instantaneously applied high input voltage is limited only by the parasitic inductance and the path resistance to the output capacitor. While most test waveforms specify some sufferable rise time, an infinite input slew rate is not inconceivable, such as might arise during bench testing. Q3 is added to give the LT4356's current limit loop a head start under these conditions.

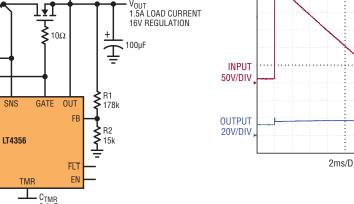

Figure 5 shows the results of the circuit subjected to a 300v spike. CTMR is sized to ride through such excursions, but longer duration surges will be interrupted, thereby protecting the MOSFETs from certain destruction.

## Figure 4. 16V overvoltage regulator capable of blocking 300V transients

Q2

FDB33N25

lŧI

**ξ**10Ω

D3

N4148

RSNUB 51Ω

D4

1N756A

0.039µF

10k

C<sub>SNUB</sub> 0.01µF

**ξ**100Ω

้ Q3

2N3904

Ŧ

R<sub>SNS</sub>

33mO

SNS

Ŧ '0.1μF

V<sub>CC</sub>

GND

SHDN

Аоит IN+

Figure 5. Results of 300V spike on input of circuit in

Figure 4

## 2ms/DIV