# Arria 10 Low Profile PCIe FPGA Board

The 385A low profile accelerator card provides a powerful PCIe computing and I/O platform for FPGA development and deployment across a range of application areas including high performance computing, image processing, and network analytics.

### Tool Flow Flexibility for Softwareor Hardware-Based Development

**FPGA** Tools

- $\cdot$  Abstration for faster development

- $\cdot$  Push-button flow for FPGA

- executable, driver, and API

- Add optimized HDL IP cores to OpenCL designs as libraries

- · Hand-code for ultimate performance

- High-Level Synthesis (HLS) available for rapid development

- FPGA card designed to support standard Intel IP cores for Stratix 10

# **Additional Services**

Take advantage of BittWare's range of design, integration, and support options

Customization Additional specification options or accessory boards to meet your exact needs.

## Server Integration Available pre-integrated in our <u>TeraBox servers</u> in a

range of configurations.

| Application<br>Benchmark<br>Report | ~                  |

|------------------------------------|--------------------|

| nega Accession of Lation Bo        | damant using OpenG |

|                                    |                    |

Application Optimization Ask about our services to help you port, optimize, and benchmark your application.

Service and Support BittWare Developer Site provides online documentation

and issue tracking.

**Board Specifications**

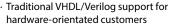

| FPGA               | <ul> <li>Intel Arria 10 GX</li> <li>1150 GX F1517 NF40 package</li> <li>Core speed grade -2: I/O speed grade -3</li> <li>Contact BittWare for other Arria 10 GX options</li> </ul>                                                                                                                                                                                                                                                  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-board Flash     | Flash memory for booting FPGA                                                                                                                                                                                                                                                                                                                                                                                                       |

| On-board<br>memory | <ul> <li>Two banks of DDR3 SDRAM x 72 bits</li> <li>4GB per bank (8GB total /16GB and 32GB version also available)</li> <li>2133MT/s per bank</li> </ul>                                                                                                                                                                                                                                                                            |

| Host interface     | • x8 Gen3 interface direct to FPGA                                                                                                                                                                                                                                                                                                                                                                                                  |

| QSFP cages         | <ul> <li>2 QSFP+ cages on front panel connected directly to<br/>FPGA via 8 transceivers</li> <li>User programmable low jitter clocking supporting<br/>10/40 GbE</li> <li>Each QSFP can be independently clocked</li> <li>Clocking options:         <ul> <li>Network recovered with jitter attenuation</li> <li>QSFP clocking: user programmable, or CPRI,<br/>1GbE</li> <li>External clock input, 1PPS input</li> </ul> </li> </ul> |

| Cooling            | <ul> <li>Standard: single-width active heatsink<br/>(embedded fan)</li> <li>Optional: single-width passive heatsink</li> </ul>                                                                                                                                                                                                                                                                                                      |

| Electrical         | <ul> <li>On-board power derived from 12V PCIe slot</li> <li>Power dissipation is application dependent</li> <li>Typical max power consumption 75W</li> </ul>                                                                                                                                                                                                                                                                        |

| Environmental | Operating temperature: 5°C to 35°C                                                                    |

|---------------|-------------------------------------------------------------------------------------------------------|

| Quality       | <ul><li>Manufactured to ISO9001:2008 IPC-A-610-Class</li><li>RoHS compliant</li></ul>                 |

| Form factor   | <ul> <li>Half-height, half-length PCle single-slot board</li> <li>167.6mm x 68.9 mm x 17mm</li> </ul> |

### **Development Tools**

| FPGA<br>development | BIST - Built-In Self-Test for CentOS 7 provided with<br>source code (pinout, gateware, PCIe driver & host test<br>application) |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Application         | Supported design flows - Intel FPGA OpenCL SDK,                                                                                |

| development         | Quartus Prime Pro (HDL, Verilog, VHDL, etc.)                                                                                   |

#### **Deliverables**

- 385A FPGA board

- USB cable (front panel access)

- Built-In Self-Test (BIST)

- OpenCL HPC Board Support Package (BSP)

- 1-year access to online Developer Site

- 1-year hardware warranty

## To learn more, visit www.BittWare.com

Rev 2019.04.03 | April 2019

© BittWare 2019

Arria 10 is a registered trademark of Intel Corp. All other products are the trademarks or registered trademarks of their respective holders.