Mit der fortlaufenden Branchenmigration von Bereichen wie E-Commerce, Remote-Arbeit und Cloud-Computing steigen die Ansprüche an Rechenzentren, weiterhin exponentiell zu wachsen.

DDR4-Standard-DRAM wurde seit der Einführung im Jahr 2014 breit angenommen. Steigende Benutzerbedürfnisse in den Bereichen Zuverlässigkeit, Verfügbarkeit und Wartbarkeit haben es in den letzten Jahren jedoch offensichtlich gemacht, dass eine neue DRAM-Generation benötigt wird. Kürzlich verkündete Micron Technology, Inc ein umfassendes Programm zur Technologieförderung (Technology Enablement Program, TEP), um das Entwerfen, die Entwicklung und die Qualifikation von Computing-Plattformen der nächsten Generation, die DDR5-DRAM verwenden (die fortschrittlichste derzeit verfügbare Technologie), zu unterstützen.

Im Januar 2020, kündete Micron das Erscheinen von DDR5-RDIMM-Modellen an. Im Juli 2020 veröffentlichte JEDEC (die globale Normungsorganisation für die Elektronikindustrie) den von vielen erwarteten JESD79-5-DDR5-SDRAM-Standard. Aufgrund ihrer Erfahrungen mit den technischen Feinheiten des neuen DRAM und ihrem Engagement mit den neuen Standard existieren Unternehmen wie Micron, Cadence, Montage, Rambus, Renesas und Synopsys an der Schnittstelle von Marktanforderungen und technischer Entwicklung. Mit dem TEP arbeiten diese Gruppen von Geschäften Hand in Hand mit Kanalpartnern wie Distributoren, Mehrwert-Wiederverkäufern und OEMS, während sie mit neuer Technologie neue Produkte entwickeln.

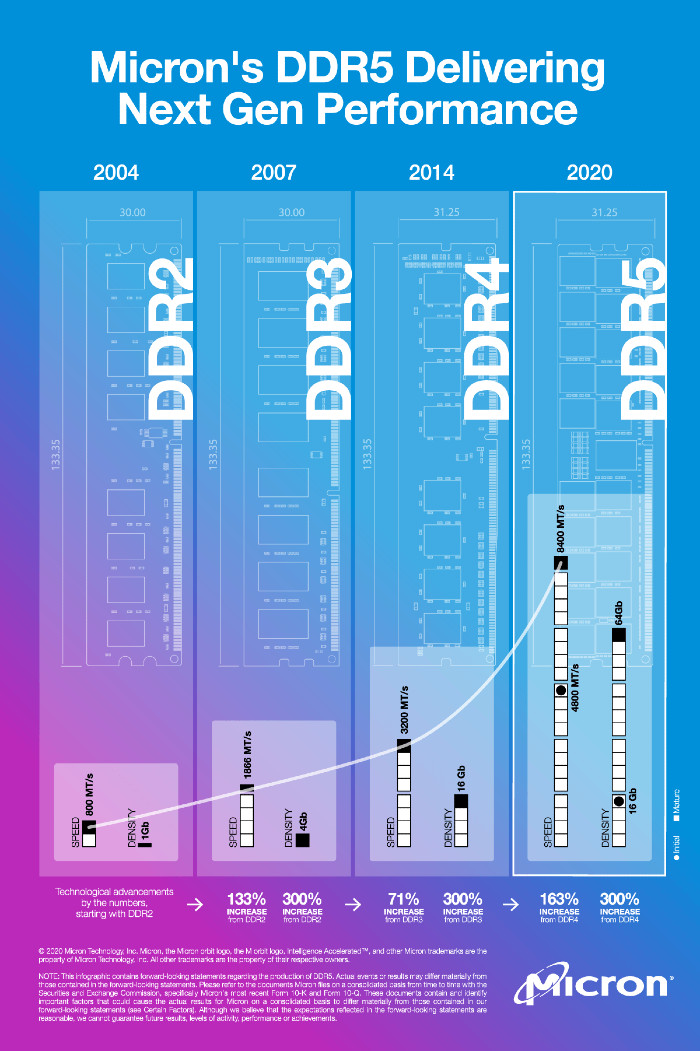

DDR5 ist heute der technologisch fortschrittlichste DRAM. Aufbauend auf der branchenführenden 1-znm-Prozesstechnologie von Micron, liefert DDR5 eine Steigerung von 85 % bei der Speicherleistung. Der Schlüssel zu dieser Entwicklung ist die Speicherdichte – DDR5 verfügt hier über das Doppelte im Vergleich zum Vorgänge DDR4. In dieser Infografik sehen Sie die exponentiellen Geschwindigkeitssteigerungen des DRAM im Laufe der Zeit, und wie DDR5 bisher am besten ist.

Diese Evolution der Geschwindigkeit ermöglicht eine erhöhte Speicherbandbreite und ‑Kapazität, die von Rechenzentren auf dem neuesten Stand der Technik mit schnell wachsenden Zahlen von Prozessorkernen benötigt werden. Die Tabelle unten präsentiert eine Übersicht der Vorteile des DDR5:

| Eigenschaft/Meinung | DDR4 | DDR5 | DDR5-Vorteil | |||

| Datenraten | 1600-3200 MT/s | 3200-6400 MT/s | Erhöht die Leistung und Bandbreite | |||

| VDD/VDDQ/VPP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | Senkt den Energieverbrauch | |||

| VREF, intern | VREFDQ | VREFDQ, VREFCA, VREFCS | Erhöht Spannungsmargen, reduziert BOM-Kosten | |||

| Gerätedichten | 2 Gbit - 16 Gbit | 8 Gbit - 64 Gbit | Ermöglicht größere monolithische Geräte | |||

| Voreinstellung | 8n | 16n | Hält den internen Kerntakt niedrig | |||

| DQ-Empfängerentzerrung | CTLE | DFE | Verbessert das Öffnen der erhaltenen DQ-Datenaugen im DRAM | |||

| Anpassung des Arbeitszyklus (Duty Cycle Adjustment, DCA) | Keine | DQS und DQ | Verbessert das Signalisieren für weitergeleitete DQ/DQS-Pins | |||

| Interne DQS-Verzögerung Überwachung |

Keine | DQS-Intervall-Oszillator | Erhöht die Robustheit gegenüber Umweltveränderungen | |||

| On-die-ECC | Keine | 128-b + 8‑b-SEC, Fehlerprüfung und Bereinigung | Stärkt On-Chip-RAS | |||

| CRC | Schreiben | Lesen/Schreiben | Stärkt das System-RAS durch Schutz des Lesens von Daten | |||

| Bankgruppen (BG)/Banken | 4 BG x 4 Banken (x4/x8) 2 BG x 4 Banken (x16) |

8 BG x 2 Banken (8 Gbit x4/x8) 4 BG x 2 Banken (8 Gbit x 16) 8 BG x 4 Banken (16 - 64 Gbit x4/x8) 4 BG x 4 Banken (16 - 64 Gbit x 16) |

Erhöht Bandbreite/Leistung | |||

| Befehls‑/Adressschnittstelle | ODT, CKE, ACT, RAS, CAS, WE, A |

CA<13:0> | Reduziert die Anzahl der CA-Stifte drastisch | |||

| ODT | DQ, DQS, DM/DBI | DQ, DQS, DM, CA bus | Erhöht Signalintegrität, reduziert BOM-Kosten | |||

| Burst-Länge | BL8 (und BL4) | BL16, BL32 (und BC8 OTF, BL32 OTF) |

Ermöglicht 64B-Cache-Zeilenabruf mit nur 1-DIMM-Unterkanal. | |||

| MIR („Spiegel“-Stift) | Keine | Ja | Verbessert DIMM-Signalisierung | |||

| Bus-Inversion | Daten-Bus-Inversion (DBI) | Befehls‑/Adressinversion (CAI) | Reduziert VDDQ-Rauschen auf Modulen | |||

| CA-Training, CS-Training | Keine | CA-Training, CS-Training | Verbessert die Zeitspanne für CA‑ und CS-Stifte | |||

| Trainingsmodi für das Leveling schreiben | Ja | Verbessert | Entschädigt für unpassenden DQ-DQS-Pfad | |||

| Trainingsmuster lesen | Möglich mit MPR | Dedizierte MRs für Serien (benutzerdefiniert), Uhr und LFSR -generierte Trainingsmuster |

Sorgt für eine robustere Lese-Timing-Marge | |||

| Modus-Register | 7 x 17 Bits | Bis zu 256 x 8 Bits (LPDDR-Typ lesen/schreiben) |

Bietet Raum zur Erweiterung | |||

| PRECHARGE-Befehle | Alle Banken und pro Bank | Alle Banken, pro Bank und dieselbe Bank | PREsb ermöglicht vorgebührenspezifische Bank für jeden BG | |||

| REFRESH-Befehle | Alle Banken | Alle Banken und dieselbe Bank | REFsb ermöglicht die Aktualisierung einer bestimmten Bank für jeden BG | |||

| Rückschleifmodus | Keine | Ja | Ermöglicht das Testen der DQ‑ und DQS-Signalisierung |

Vorteile des DDR5-Programms zur Technologieförderung (TEP) von Micron:

Zugelassene Partner können Zugang erhalten zu:

– Technischen Ressourcen wie Datenblätter, elektrische, thermische und Simulationsmodelle zur Unterstützung bei der Produktentwicklung und dem Plattformaufbau.

– Bestimmten DDR5-Komponenten und Modulmodellen, wenn diese verfügbar sind.

– Verbindungen mit anderen Ökosystem-Partnern, die bei der Entwicklung und dem Aufbau der DDR5-aktivierten-Plattformen unterstützen.

– Technische Unterstützung und Trainingsmaterialien.

Den technischen Überblick erhalten

Pressemitteilung herunterladen