Ingenieure entscheiden sich aufgrund der größeren Effizienz, der Leistungsdichte und der insgesamt besseren Systemkosteneffizienz heute mehr als je zuvor für Siliziumkarbid (SiC)-basierte Produkte statt für Silizium (Si)-basierte Komponenten.

Ingenieure müssen nicht nur die Basisgrundsätze für das Design, die für SiC- und Si-Geräte gleich sind, und die spezifischen Eigenschaften, Kapazitäten und Vorteile von SiC-Geräten berücksichtigen. Sie müssen auch Modelle erstellen und Simulationen durchführen, um sicherzustellen, dass ihre Designziele erfüllt werden.

Wie für Si-Geräte sind nun auch für SiC-Geräte optimierte Tools und Modelle verschiedener Anbieter verfügbar. Außerdem können standardmäßige Modellierungsminderungen angewendet werden. Auch wenn es Unterschiede zwischen Tools wie LTSpice, PLECS und dem SpeedFit 2.0 Design Simulator™ von Wolfspeed gibt, helfen Ihnen die Tipps der Wolfspeed-Experten bei der Durchführung genauer Simulationen für SiC-Geräte.

Statische Simulation mit LTSpice

Die Spice-Modelle von Wolfspeed sind für Temperaturen von 25 °C und 150 °C optimiert. Der Body-Dioden-Betrieb ist für eine Treiberspannung (VGS) von – 4 V für Geräte der 3. Generation und – 5 V für Geräte der 2. Generation optimiert. Ingenieure können Funktionen für Selbsterwärmung, vorübergehende thermische Beanspruchung und parasitäre Induktanz integrieren. Parasitäre bipolare und verbundene Effekte, lawinenartige Multiplizierungsprozesse und die Abhängigkeit der Schaltspannung der Body-Diode von der Gate-zu-Quellenspannung werden jedoch nicht modelliert.

Die Ergebnisse statischer LTSpice-Simulationen – die IV-Kurve bei verschiedenen VGS-Werten und die Body-Dioden-Kurve – stimmen gut mit den tatsächlichen Messungen überein. Im Fall von Kapazitäten – Eingangskapazität (Ciss), Ausgangskapazität (Coss) und Rückübertragungskapazität (Crss) – erfüllen die Ergebnisse statischer Simulationen ihren Zweck ebenfalls ziemlich gut. Ingenieure können sich daher auf die statischen Parameter der Spice-Modellierung verlassen.

Ein Doppelpulstest

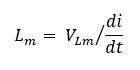

Halbbrücken-Doppelpulstests sind typische Vergleichstests zur Charakterisierung des dynamischen Verhaltens. Wenn eine Simulation ohne Berücksichtigung bestimmter Aspekte modelliert wird, beispielsweise parasitärer Einflüsse, weichen die Ergebnisse erheblich von den gemessenen tatsächlichen Ergebnissen ab (Abbildung 1). Da der Energieverbrauch Auswirkungen auf die Effizienz hat, wirken sich diese großen Abweichungen erheblich auf die thermischen Berechnungen aus.

Abbildung 1: Schaltverlustergebnisse in einer idealen Doppelpulstest-Simulation

liegen um ungefähr 45 % unter den Werten im Datenblatt für DUT, U2.

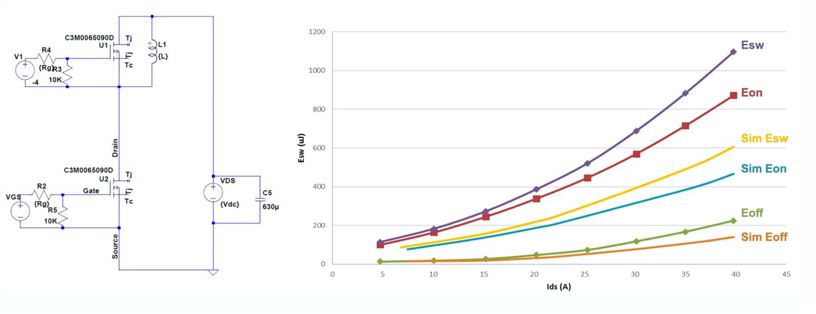

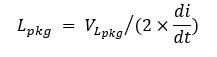

Im Testfall wird ein langer Impuls von einer Lücke von 1 µs gefolgt. Anschließend wird in kurzer Impuls gesendet. Einschalt- und Ausschaltzeit werden konventionell wie bei Si-basierten Geräten gemessen. Eine genauere Betrachtung der Wellenformen (Abbildung 2) zeigt den Unterschied zwischen den tatsächlichen Ergebnissen und den Ergebnissen der idealen Simulation. Die Anstieg- und Abfallzeiten sind in der Simulation sehr viel kürzer als in der Messung, da sich auf die tatsächlichen Ergebnisse Induktanzen auswirken – die parasitäre Streuinduktanz (Lm) zwischen den beiden Geräten und die Gehäuseinduktanz (Lpkg), die Quellinduktanz des Gehäuses. Darüber hinaus gibt es einen Unterschied zwischen den Überschreitungsergebnissen für Einschalt- und Ausschaltzeit. Diese Unterschiede tragen zum Unterschied beim Schaltverlust insgesamt bei.

Abbildung 2: Ein Vergleich der Wellenformen, der zeigt, dass die tatsächliche Anstiegszeit

39 ns beträgt, während die simulierte Anstiegszeit lediglich 22,83 ns beträgt. Die tatsächliche

Abfallzeit beträgt 20 ns im Vergleich zu 13,63 ns in der Simulation.

Um ein genaues Modell zu erstellen, müssen die Induktanzen extrahiert und manuell in LTSpice importiert werden. Das thermische Modell in PLECS berücksichtigt hingegen keine parasitären Komponenten.

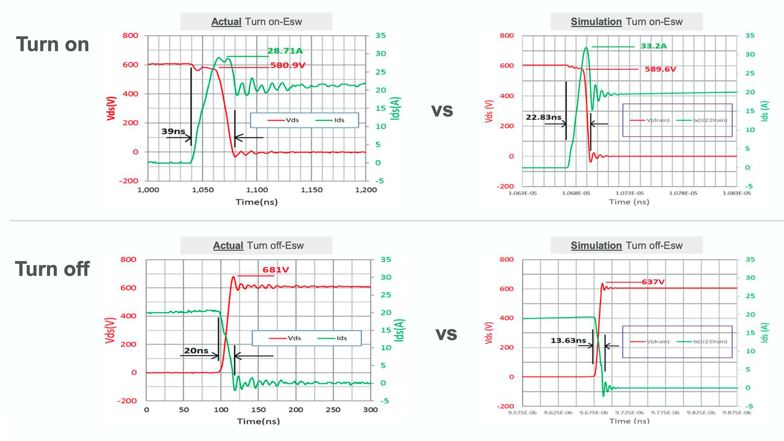

Suche von Lm

|

Lm ist die Induktanz zwischen der Quelle des High-

Wobei: Dies ergibt den Wert 23,1674 nH für Lm.

|

Abbildung 3: Aus der tatsächlichen Wellenform extrahierte Daten können für die Berechnung von Lm verwendet werden. |

Ob synchroner Anfall, synchroner Anstieg, Halbbrücke oder Vollbrücke – das Design verwendet wahrscheinlich eine Konfiguration mit High-Side- und Low-Side-Geräten über eine Leiterplatte (PCB). Bei Befolgung bewährter Layoutverfahren befindet sich Lm im Bereich zwischen 20 nH und 25 nH. Ingenieure können dies in Simulationen als Faustregel betrachten.

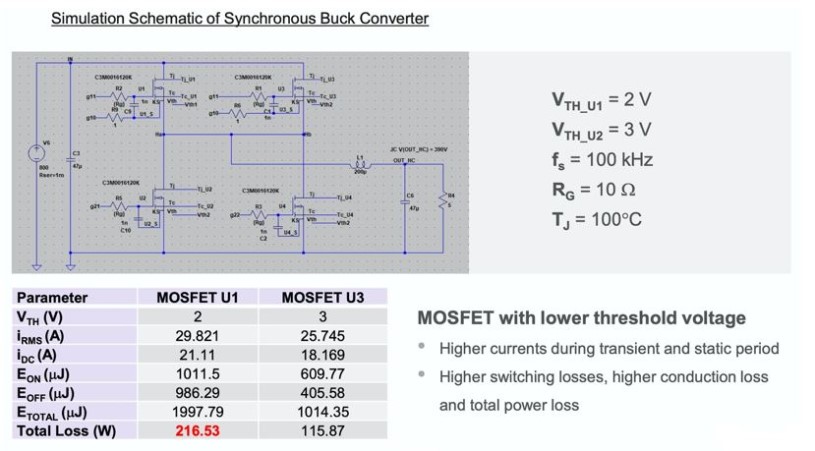

Extrahieren von Lpkg

Designer erwarten möglicherweise, dass Lpkg für Standardgehäuse wie das TO-247 bei allen Anbietern identisch ist. Es gibt jedoch aufgrund von Unterschieden bei der Dicke der Leiterrahmen, bei den Quell-Bonddrähten und bei der Länge des Gehäuserands Abweichungen. Wenn der Wert im Datenblatt angegeben ist, kann er leicht für das Modell berücksichtigt werden. Wenn er nicht enthalten ist, kann er aus einer gemessenen Wellenform extrahiert und extrapoliert werden, um eine gute Schätzung für das vorliegende Gehäuse zu erhalten.

Wobei:

VLpkg = Vds – VLds + Vdson = – 11,515 V

Lds = 6,5372 nH aus dem Spice-Modell,

Vds = ~ – 27,8 V aus der tatsächlichen Wellenform,

VLds = – 15,035 V,

Vds_on @ 20 A = 1,25 V aus dem C3M0065090D-Datenblatt und

di/dt = – 2,3 x 109

Abbildung 4: Durch die Hinzufügung der berechneten Induktanzen zum LTSpice-

Modells ist das Modell nun nahe an den tatsächlichen Messungen.

In unserem Beispiel erhalten wir einen Lpkg-Wert von 2,503 nH. Trotz Abweichungen kann dieser Wert als eine gute Schätzung und eine zuverlässige Faustregel betrachtet werden. Die Durchführung der Simulation unter Berücksichtigung der Induktanzen führt zu einem genauen dynamischen Modell (Abbildung 4).

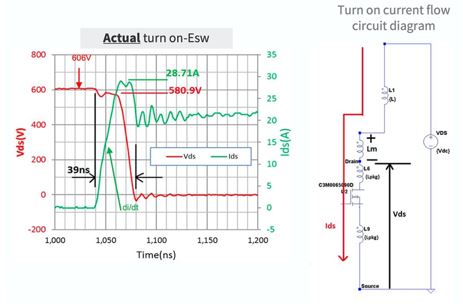

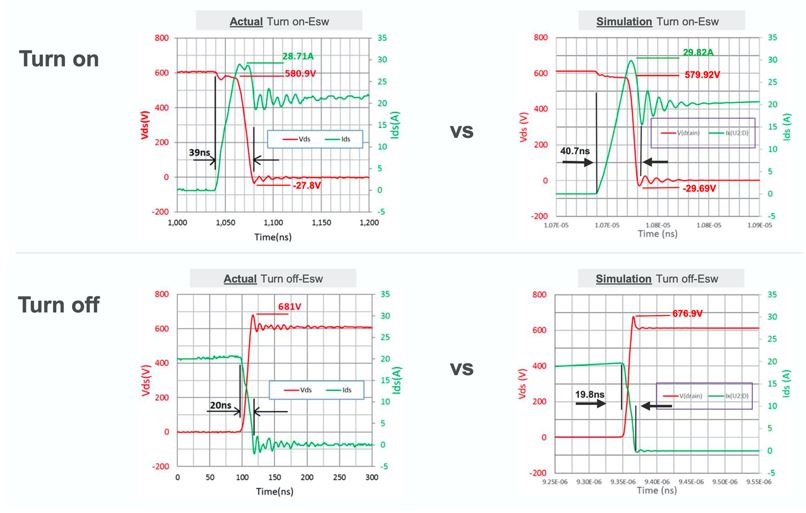

Nach Berücksichtigung der Induktanzen liegen die Werte für die Gesamtschaltenergie (Esw) sowie Eon and Eoff für den tatsächlichen und den simulierten Doppelpulstest sehr nahe beieinander (Abbildung 5).

Abbildung 5: Nach der Einrichtung parasitärer Einflüsse stimmen die

simulierten Schaltverluste mit den Angaben im C3M0065090D-Datenblatt überein.

Bei Anwendung dieser Faustregel für Lm und Lpkg erhalten Ingenieure ziemlich genaue Verlust- und thermische Berechnungen für die Wärmebilanz.

Parallele MOSFETs

SiC MOSFETs werden häufig parallel angeordnet, um Stromtragfähigkeit und Leistungswerte zu verbessern. Hier müssen jedoch einige Aspekte berücksichtigt werden:

- • Stromungleichheiten aufgrund von Unterschieden bei der Schwellenspannung, VTH

- • Stromungleichheiten aufgrund asymmetrischer parasitärer Induktanzen

- • Gate-Treiber-Schwingung

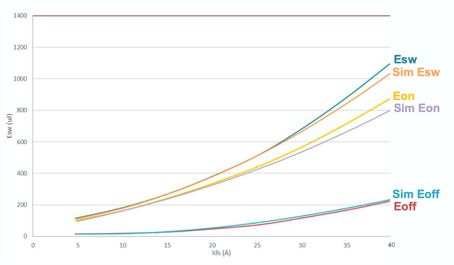

Im Fall von Wolfspeed SiC MOSFETs ist die Wahrscheinlichkeit für Ungleichheiten bei Geräteeigenschaften gering. Ingenieure müssen jedoch möglicherweise weitere SiC-Komponenten mit einer höheren Spezifikationstoleranz verwenden und wählen daher beispielsweise ein Gerät mit einem VTH von 2 V und ein anderes Gerät mit 3 V aus. Das Gerät mit dem niedrigeren Schwellenwert besitzt eine höhere Transiente, damit höhere Schalt- und Leistungsverluste und daher insgesamt höhere Leistungsverluste auf (Abbildung 6).

Abbildung 6: Der Gesamtverlust des 2-V-Geräts ist beinahe zweimal so hoch wie der

des 3-V-Geräts aufgrund der Stromungleichheit.

Auch wenn beide Geräte den gleichen Gate-Widerstand (RG) aufweisen und bei gleicher Temperatur und Schaltfrequenz betrieben werden, führt eine Modellierung ohne Berücksichtigung dieser Aspekte dazu, dass U1 einen Gesamtverlust von mehr als 200 W und U3 einen Gesamtverlust von etwas mehr als 100 W aufweist. Simulierte Wellenformen zeigen, dass U1 einen Spitzen-Überschusswert von ungefähr 70 A erreicht, bevor der Wert auf stabile 50 A abfällt. Der Spitzenwert von U3 liegt bei ungefähr 49 A und fällt dann auf stabile 30 A ab. Daher besteht ein beträchtlicher Unterschied bei der Stromtragfähigkeit zwischen den beiden Geräten. Außerdem bestehen geringe Unterschiede bei den Einschalt- und Ausschaltzeiten.

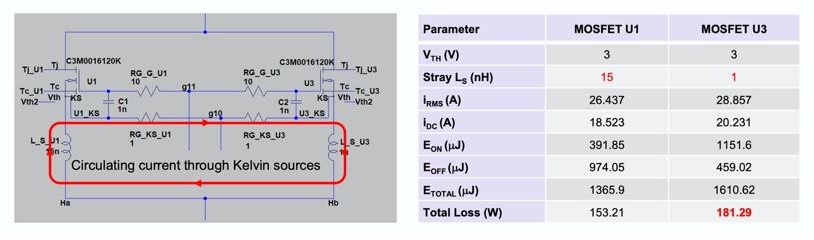

Die zweite Ursache für Stromungleichheiten sind asymmetrische parasitäre Einflüsse. Angenommen, zwei Geräte, U1 und U3 (Abbildung 7) besitzen den gleichen VTH, jedoch unterschiedliche Quellinduktanzen. Dies führt zu erheblichen Ungleichheiten bei di/dt-Werten, Spannungen über die Streuinduktanz, Gate-Treibern und Drain-Strömen. Simulierte Wellenformen zeigen, dass der Strom für U3 sehr viel schneller ansteigt und abfällt und höhere Werte für IDC und IRMS erreicht. Dies führt zu einem um 17,9 % höheren Schaltverlust und zu einem um 18,3 % höheren Gesamtverlust für dieses MOSFET-Gerät.

Abbildung 7: Der Unterschied zwischen der Streuinduktanz Ls für U1

und U3 wird in diesem Beispiel übertrieben dargestellt, um

die Auswirkungen der Ungleichheiten zu zeigen.

Minderung von Ungleichheiten durch ein gutes Design

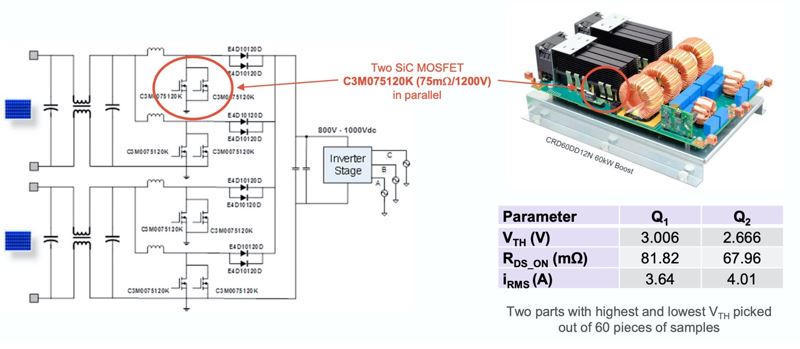

Die Auswirkungen von MOSFETs mit Ungleichheiten können durch die Berücksichtigung bewährter Designverfahren erheblich reduziert werden. Dies kann anhand des Referenzdesigns CRD60DD12N für einen 60-kW-Solarstrominverter gezeigt werden, in dem zwei C3M075120K-MOSFETs mit 75 mΩ und 1.200 V parallel verwendet werden (Abbildung 8). Auch die Verwendung von zwei TO-247 MOSFETs mit 4 Leitungssätzen, die in einer Gruppe von 60 Komponenten den höchsten und niedrigsten VTH aufweisen, führt bei Anwendung bewährter Designverfahren zu einer gut funktionierenden Hardware.

Abbildung 8: Trotz der Unterschiede bei VTH werden die Auswirkungen

von Geräteungleichheiten in diesem Testschaltkreis minimiert.

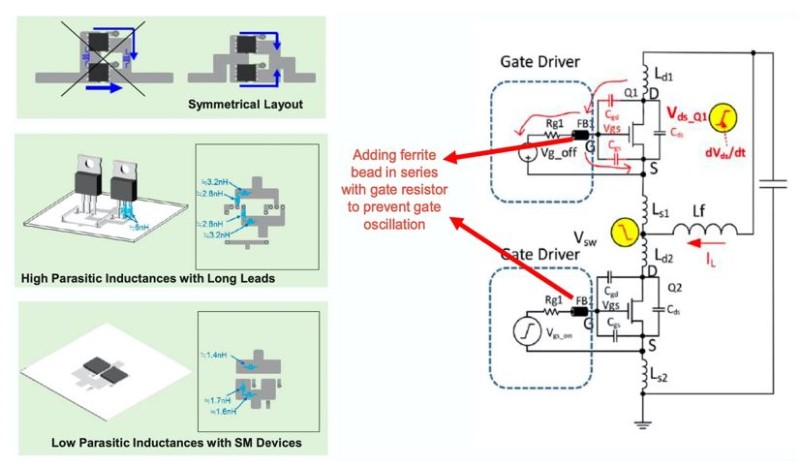

Ein symmetrisches PCB-Layout hat kritische Bedeutung für die Reduzierung des Kreisstroms in den Gate-Schleifen paralleler Schalter. Trennen Sie die Stromschleife von der Gate-Schleife, stellen Sie eine ausreichende Dämpfung bereit, um eine Gate-Schwingung zu verhindern, und fügen Sie am Gate-Fuß eine Ferritperle hinzu, um Spannungsspitzen und Nachschwingungen am Gate zu reduzieren, wodurch Komponenten beschädigt werden könnten (Abbildung 9).

Abbildung 9: Bewährte Designverfahren – streng symmetrisches Layout, ausgeglichenes

Signal, Trennung von Strom- und Gate-Schleifen, Dämpfung zur Verhinderung von

Gate-Schwingungen und ein kleiner RG mit Ferritperle zur Reduzierung von Nachschwingungen –

alles zusammen reduziert Stromungleichheiten.

Mithilfe dieser Designverfahren trägt Q1 im Testschaltkreis 47,6 % des gesamten Stroms. Q2 trägt 52,4 % und erreicht akzeptable realistische Ergebnisse trotz Geräteungleichheiten.

Größere Tool-Auswahl

SiC-basierte Designs können mithilfe von SpeedFit, LTSpice oder PLECS von Wolfspeed modelliert werden. Während SpeedFit und LTSpice nach der Registrierung bei Wolfspeed kostenlos verwendet werden können, fallen für PLECS Abonnementkosten an. Die Unterschiede zwischen den Tools beziehen sich auf die Art, wie Simulationen generiert werden, und auf die Einschränkungen für Simulationen, beispielsweise die Behandlung von parasitären Einflüssen und die Berechnung von Verlusten.